Часть 1. PDP и VAX

Digital Equipment Corporation (сокращенно DEC), основанная в 1957 двумя инженерами, Кеннетом Ольсеном (Kenneth Olsen) и Харланом Андерсоном (Harlan Anderson), выпускниками Массачусетского технологического института, была одной из старейших и наиболее значимых компаний мировой компьютерной индустрии.

До основания компании, Ольсен работал в Линкольнской лаборатории при том же институте, содержащейся на средства Министерства обороны США, и участвовал в разработке одного из первых транзисторных компьютеров, TX-2. Первое время компания разрабатывала и продавала элементарные модули для вычислительной техники, но уже в 1960 представила свой первый компьютер, 18-битный PDP-1 (Programmable Data Processor - 1), способный производить около 100 тыс. операций в секунду; кроме всего прочего, именно на нем была написана первая в истории компьютерная игра, Spacewar Стивена Рассела (Steven Russell). 12-битный PDP-8, запущенный в производство в 1964, вполне заслуженно считают первым серийно выпускаемым "миникомпьютером", из-за довольно компактных размеров (с небольшой шкаф) и невысокой, по тем временам, цены (около 18 тыс. долл. США (1965) в базовой комплектации); благодаря отличному соотношению цены и производительности, этот компьютер смог составить достойную конкуренцию знаменитым мэйнфрэймам IBM, и к 1968 было собрано около 1450 машин (не считая поздних многочисленных модификаций). В том же 1968 был представлен 36-битный PDP-10, основанный на дизайне экспериментального PDP-6, рассчитанный на использование в центрах обработки данных, исследовательских лабораториях, и в военных целях; модификации PDP-10 производились вплоть до 1983. Работы над усовершенствованием 36-битной архитектуры продолжались в рамках проекта "Единорог" (the Unicorn project), под руководством Леонарда Хьюджеса (Leonard Hughes) и Дэвида Роджерса (David Rogers), но в июне 1975 проект был закрыт, и все ресурсы были переведены на поддержку другой, 32-битной, архитектуры.

16-битный PDP-11, запущенный в производство в начале 1970-х, был первым компьютером DEC, в котором использовались 8-битные байты, и прямым наследником линейки PDP-8. Благодаря простой и удачной архитектуре, основанной на системной шине Unibus (или её модификации, Q-bus), довольно эффективному набору инструкций, и, что немаловажно, невысокой стоимости, линейка PDP-11 очень быстро обрела популярность. Вполне закономерно, что PDP-11 вскоре стали широко клонировать, в том числе и в "странах народной демократии": СМ-4 (СССР, Болгария, Венгрия), СМ-1420 (СССР, Болгария, ГДР), СМ-1600 (СССР), ИЗОТ-1016 (Болгария), ДВК (СССР). Для PDP-11 было разработано множество операционных систем: DEC предлагала P/OS, RSX-11, RT-11, RSTS/E, также было доступно несколько вариантов DOS, и в конце-концов, на PDP-7 и PDP-11 в 1971 было сделано первое издание ОС UNIX (в Bell Laboratories), тогда ещё на ассемблере. PDP-11 ушел с рынка в течение 1980-х по одной, но неизбежной причине: недостаточный объем адресного пространства, знаменовавший переход на новую, 32-битную, но все ещё CISC, архитектуру.

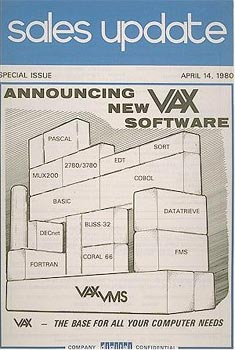

И ей стала VAX (Virtual Address eXtension), официально утвержденная на заседании VAX Architecture Committee в апреле 1975. Детали архитектуры разрабатывались в течение нескольких месяцев в рамках проекта "Звезда" (the Star project) под руководством Гордона Белла (Gordon Bell), параллельно с вышеупомянутым проектом "Единорог", и по окончании работ над обоими проектами было решено отменить дальнейшее развитие 36-битных систем, и сконцентрировать ресурсы на поддержке 32-битных VAX'ов. Фактическим результатом работы проекта "Звезда" было обоснование необходимости как увеличения разрядности основных регистров PDP-11 до 32 бит, так и их числа (с 8 до 16), а также существенный пересмотр набора инструкций. В октябре 1977 был анонсирован первый представитель линейки -- модель 11/780, а в феврале 1978 была выпущена новая операционная система для VAX'ов, VMS (Virtual Memory System) версии 1.0; к слову, новая ОС, многопользовательская и многозадачная, поддерживала до 64Мб оперативной памяти, встроенные сетевые возможности (DECnet), адаптивный планировщик задач, расширенное управление процессами, и многие другие функции, значительно опередившие свое время. В апреле 1980 вышла версия 2.0, с многочисленными улучшениями, переименованная в VAX/VMS. На VAX также была вскоре портирована классическая UNIX. VAX'ы выпускались и продавались с большим успехом в течение 1980-х, и даже на рубеже веков поставлялись ограниченными партиями по спецзаказам. Модельный ряд насчитывал несколько десятков наименований: от довольно компактных рабочих станций до 6-процессорных серверов мэйнфрэйм-класса. И по сей день тысячи VAX'ов работают в структуре Министерства обороны США и NSA (National Security Agency), а также во многих коммерческих организациях. Но тем не менее, эпоха VAX'ов осталась в 1980-х, а в 1990-х DEC сделала ставку на новую архитектуру.

Часть 2. Проект PRISM

В начале 1980-х DEC была на вершине финансового могущества, в значительной мере благодаря стабильно растущим объемам поставок VAX'ов. Однако ничто не вечно, и было очевидно, что в своё время и VAX придется уйти с рынка, как это уже происходило с PDP-11. В то время многие компании начали обращать внимание на перспективные разработки в среде RISC, и DEC явно не желала остаться в стороне. С 1982 по 1985 в составе компании активно работали несколько подразделений, занимавшихся исследованиями в области RISC:

Titan, высокоскоростной дизайн от Западной исследовательской лаборатории (Western Research Laboratory, DECwest) в Пало-Альто (Калифорния), под руководством Фореста Бэскетта (Forest Baskett), с 1982;

SAFE (Streamline Architecture for Fast Execution), под руководством Алана Котока (Alan Kotok) и Дэвида Орбица (David Orbits), с 1983;

HR-32 (Hudson RISC 32-bit), при фабрике DEC в Хадсоне (Массачусетс), под руководством Ричарда Витека (Richard Witek) и Дэниела Добберпуля (Daniel Dobberpuhl), с 1984;

CASCADE Дэвида Катлера (David Cutler) в Сиэттле (Вашингтон), с 1984.

В 1985, с подачи Катлера насчёт создания "корпоративного RISC-плана", все 4 проекта были объединены в один,PRISM(Parallel Instruction Set Machine), и совместными усилиями к августу 1985 была подготовлена первая спецификация на новый RISC-процессор. Стоит упомянуть, что к тому времени DEC уже принималa активное участие в разработке процессора MIPS R3000 и даже инициировалa создание консорциума Advanced Computing Environment для продвижения этой архитектуры на рынке.

Поэтому нет ничего удивительного в том, что разрабатываемый процессор унаследовал много черт, присущих архитектуре MIPS, но в то же время отличия были очевидны. Все инструкции имели фиксированную длину в 32 бита, из них верхние 6 и нижние 5 были собственно кодом инструкции, а остальные 21 предназначались для непосредственно данных либо их адресации. Были определены 64 основных 32-битных целочисленных регистрa (MIPS предусматривалa 32), а также 16 дополнительных 64-битных векторных регистров, и 3 контрольных регистра для векторных операций: два 7-битных (vector length и vector count), один 64-битный (vector mask). Регистр состояния процессора отсутствовал, поэтому результат сравнения двух скалярных операндов помещался в целочисленный регистр, а результат сравнения двух векторных операндов -- в vector mask. Встроенный блок вычислений с плавающей запятой не предусматривался. Также присутствовал набор специальных инструкций(Epicode, или extended processor instruction code), реализованных программно посредством загружаемого микрокода, для облегчения решения специальных задач, присущих определённой среде или операционной системе, и не предусмотренных стандартным набором команд; впоследствии, эта функция была реализована в архитектуре Alpha под названиемPALcode(Privileged Architecture Library code).

К 1988 проект был всё ещё в стадии разработки, когда высший менеджмент DEC закрыл его, посчитав дальнейшее финансирование нецелесообразным. Протестуя против этого, Катлер уволился и ушёл в Microsoft, где возглавил подразделение по разработке Windows NT.

В начале 1989 DEC представила свои первые рабочие станции с RISC-процессорами, DECstation 3100 на основе 32-битногоMIPS R2000с частотой в 16МГц, и DECstation 2100 на основе того же процессора, но с частотой в 12МГц. Обе машины работали под ОС Ultrix и стоили довольно умеренно (около 8 тыс. долл. США (1990) за DECstation 2100).

Часть 3. Проект Alpha

В 1989 морально стареющая архитектура VAX уже с трудом могла конкурировать с RISC-архитектурами 2-го поколения, такими какMIPSиSPARC, и было вполне очевидно, что следующее поколение RISC оставит VAX немного шансов на выживание. В середине 1989 перед инженерами DEC была поставлена задача создания конкурентоспособной RISC-архитектуры с перспективным потенциалом, но минимально несовместимой с VAX, чтобы облегчить перенос на неё VAX/VMS и всей сопутствующей программной базы. Также было определено, что новая архитектура должна изначально быть 64-битной, так как конкуренты уже были в процессе перехода на 64 бита. Была создана рабочая группа, в которой главными архитекторами были Ричард Витек и Ричард Сайтс (Richard Sites).

Первое официальное упоминание об архитектуреAlphaдатируется 25 февраля 1992, на конференции в Токио. Одновременно в небольшом обзоре (для USENET-конференции comp.arch) были перечислены ключевые моменты новой архитектуры; там же было оговорено, что "Alpha" является кодовым именем нового процессора, а рыночное название будет представлено позже. Процессор имел чистую64-битнуюRISC-архитектурус инструкциями фиксированной длины(по 32 бита),с 32 целочисленными64-битными регистрами, работал с 43-битными адресами виртуальной памяти (с расширением до 64 бит в перспективе), использовал, как и VAX,little-endianпорядок следования байт (то есть, когда младший байт регистра занимает при записи младший адрес в памяти; традиционно поддерживался Intel, в противовес к big-endian, изначально внедрённому Motorola, и используемому в большинстве процессорных архитектур, где младший байт регистра занимает при записи старший адрес в памяти). Математический сопроцессор был изначально интегрирован в ядро, вместе с 32 вещественными64-битными регистрами, причём использовался произвольный доступ к ним, в отличие от примитивного стекового, используемого сопроцессорами Intel x87. Срок службы новой архитектуры был определен, как минимум, в 25 лет.

Поддерживаемый набор инструкций был максимально упрощён с целью максимального облегчения конвейеризации, и состоял из 5 групп:

инструкции для целочисленных вычислений;

инструкции для вещественных (с плавающей запятой) вычислений;

инструкции отработки условных и безусловных переходов, а также сравнения;

инструкции загрузки и сохранения данных;

инструкции PALcode.

Стоит отметить, что инструкции целочисленного деления отсутствовали, так как являлись наиболее сложными и плохо поддающимися конвейеризации, а поэтому эмулировались.

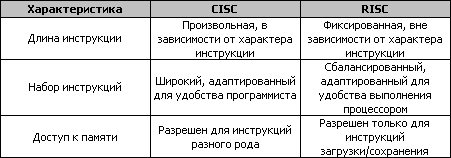

Архитектура Alpha была "настоящей" RISC (в отличие от современных процессоров архитектуры i386, которые RISC только изнутри). Концептуально разница междуRISC(Reduced Instruction Set Computing) иCISC(Complex Instruction Set Computing) состояла (и до сих пор состоит) в нескольких моментах:

Процессор предполагалось запустить в производство на очень высокой для того времени частоте - 150МГц, и довести до 200МГц при тех же конструкторских нормах. Это оказалось возможным как благодаря удачной архитектуре, так и благодаря отказу разработчиков от использования систем автоматического проектирования и выполнению всех работ по схемотехнике исключительно вручную.

Проект вступил в производственную стадию и вскоре был реорганизован в регулярное подразделение DEC.

Трудами отдела маркетинга DEC новая архитектура получила название AXP (или Alpha AXP), хотя до сих пор неизвестно, аббревиатурой чего было это недоразумение. Возможно, что и ничего; в прошлом DEC имела проблемы с торговой маркой VAX, на которую претендовала компания по производству пылесосов, и тогда дело дошло до суда. Кроме всего прочего мотивировалось, что рекламный слоган этой компании ("Nothing sucks like a Vax!" - "Ничто не сосёт так, как Vax!") дискредитирует продукцию DEC. Так что вскоре в компьютерном мире появилась шутка, что AXP - это "Almost Exactly PRISM", то есть "почти точно PRISM".

Часть 4. EV4, LCA4, EV45, LCA45

Первый процессор из семейства Alpha получил название 21064 (21 указывал, что Alpha -- это архитектура XXI века, 0 -- процессорное поколение, 64 -- разрядность в битах), и кодовое наименование EV4 (EV является [предположительно] аббревиатурой "Extended VAX", а цифра 4 -- поколением техпроцесса, CMOS4; CMOS, в свою очередь, есть аббревиатура "Complementary Metal Oxide Semiconductor"). Стоит отметить, что прототип EV4 был готов ещё в 1991, по CMOS3 техпроцессу, а поэтому с уменьшенными кэшами и без блока вычислений с плавающей запятой; тем не менее, он сыграл свою роль в отладке архитектуры и программной среды. EV4 был представлен в ноябре 1992, и поступил в производство на передовом для того времени 3-слойном 0,75µ техпроцессе (впоследствии, производство было переведено на оптическую модификацию CMOS4 -- CMOS4S, 0,675µ). Был рассчитан на напряжение питания в 3,3В, выпускался с тактовыми частотами от 150МГц до 200МГц (ТDP от 21Вт до 27Вт). Состоял из 1,68 млн. транзисторов, и имел площадь ядра в 233 кв. мм. Поддерживал многопроцессорность, как один из ключевых моментов архитектуры. Форм-фактор: PGA-431 (Pin Grid Array).

Кэш L1 был интегрирован: 8Кб для инструкций (I-cache, instruction cache), с прямым отображением (direct-mapped), а также 8Кб для данных (D-cache, data cache), с прямым отображением и сквозной записью (write-through). Задержки при чтении из D-cache составляли 3 такта. Каждая линия I-cache состояла из 32 байт инструкций, 21-битного тега, 8-битного поля истории переходов, и нескольких вспомогательных полей; каждая линия D-cache состояла из 32 байт данных и 21-битного тега. Кэш L2 (B-cache, backup cache) был рекомендуемой опцией, набирался на микросхемах синхронной или асинхронной статической памяти, работал в режиме обратной записи (write-back) с прямым отображением и упреждающим чтением (read-ahead), мог иметь размер до 16Мб (обычно от 512Кб до 2Мб); каждая линия состояла из 32 байт данных или инструкций с 1-битным long-word parity или 7-битным long-word ECC, максимум 17-битного тега с 1 битом чётности, и 3 битов состояния с 1 битом четности. Скорость чтения/записи B-cache программировалась, в тактах процессора. Разрядность системной шины данных составляла 64 или 128 бит (программируемо, с 1-битным long-word parity или 7-битным long-word ECC), и она мультиплексировалась с шиной данных B-cache, переключаясь при необходимости; разрядность системной шины адреса составляла 34 бита. Организационно B-cache был включающим (inclusive) D-cache, то есть поддерживал копию содержимого последнего. При выгрузке данных из B-cache в память использовался механизм victim write. Операции чтения/записи в B-cache являлись прерогативой исключительно процессора, для системной логики было разрешено только чтение файла тегов (B-tag, что жизненно необходимо особенно в многопроцессорных системах, для обеспечения согласованности (когерентности) кэшей).

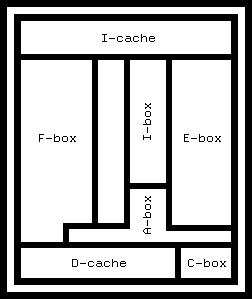

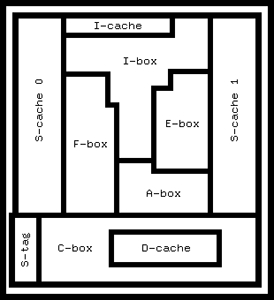

Процессор имел один целочисленный конвейер (E-box, 7 стадий), и один вещественный конвейер (F-box, 10 стадий). Декодер и планировщик инструкций (I-box) был в состоянии подавать 2 команды за такт в порядке очереди (in-order) на исполняющие устройства, то есть на E-box, F-box и блок загрузки/сохранения (A-box). Контроллер кэшей и системной шины (C-box) работал в тесном взаимодействии с A-box и управлял как интегрированными I-cache и D-cache, так и внешним B-cache. Также присутствовал блок предсказания переходов (branch prediction unit), с таблицей переходов на 4096 записей (branch history table), по 2 бита каждая. I-TLB имел 8 записей для 8Кб-страниц, и 4 записи для 4Мб-страниц, все с пoлной ассоциативностью (fully-associative). D-TLB имел 32 записи, с полной ассоциативностью.

Несмотря на отличную производительность, EV4 был довольно дорог для значительной части потенциальных покупателей, и поэтому в сентябре 1993 был анонсирован его бюджетный собрат, 21066 (LCA4, или LCA4S). Этот процессор был основан на ядре 21064, но с дополнительно интегрированными контроллерами памяти и шины PCI, а также некоторыми второстепенными функциями. Однако, разрядность системной шины данных была урезана до 64 бит, что негативно сказалось на производительности. LCA4 производился по 0,675µ CMOS4S техпроцессу, и его площадь оказалась ещё меньше, чем у EV4 (209 кв.мм по сравнению с 234 кв.мм.), а тактовые частоты были занижены (от 100МГц до 166МГц), в значительной мере из-за потенциальной угрозы перегрева в плохо вентилируемых настольных системных блоках того времени, и чтобы не создавать дополнительной конкуренции EV4. Количество транзисторов в ядре составило 1,75 млн., a напряжение питания -- 3,3В. Дизайн этого процессора был лицензирован Mitsubishi, и последняя также производила LCA4 (включая и 200МГц версию).

В октябре 1993, на Microprocessor Forum, был анонсирован 21064А (EV45), обновленная версия EV4, производимая по 4-слойному 0,5µ CMOS5 техпроцессу. В ноябре 1994, на COMDEX'94, был представлен 21066А (LCA45), почти аналогично модифицированная версия LCA4. Стоит отметить, что манера маркетологов DEC добавлять букву к модели процессора при перепланировке ядра под новый техпроцесс сохранилась и в будущем. Собственно состав процессорных ядер изменился незначительно; EV45 теперь обладал удвоенным размером кэша L1 (16Кб I-cache + 16Кб D-cache), к полям данных и тегам I-cache и D-cache было добавлено по биту чётности, поля истории переходов I-cache были расширены до 16 бит, ассоциативность D-cache была увеличена до 2 (2-way set associative), а к режимам контроля над системной шиной данных был добавлен 1-битный byte parity. Также в EV45 и LCA45 был незначительно модифицирован F-box (оптимизация деления: в EV4 одна операция требовала 34 такта для операндов одинарной точности и 63 такта для операндов двойной точности, вне зависимости от значений операндов; в EV45 она уже требовала от 19 до 34 тактов для операндов одинарной точности и от 29 до 63 тактов для операндов двойной точности, в зависимости от значений операндов). LCA45 также производился на мощностях Mitsubishi. Площади ядер уменьшились: до 164 кв.мм (EV45) и до 161 кв.мм (LCA45), количество транзисторов в ядре EV45 возросло до 2,85 млн., а в ядре LCA45 осталось прежним (1,75 млн.). В конечном результате, энергопотребление обоих процессоров в расчёте на единицу частоты сократилось, хотя напряжение питания осталось неизменным (3,3В). Тактовые частоты ЕV45 составляли от 200МГц до 300МГц (TDP от 24Вт до 36Вт), LCA45 -- от 166 до 233МГц.

Так как DEC участвовала в разработках оборудования под заказ Министерства обороны США, то в 1994 были спроектированы процессоры 21068 (66МГц) и 21068А (100МГц), являвшиеся вариантами LCA4 и LCA45, адаптированными под военные нужды (пассивное охлаждение, жёсткие температурные условия, пр.).

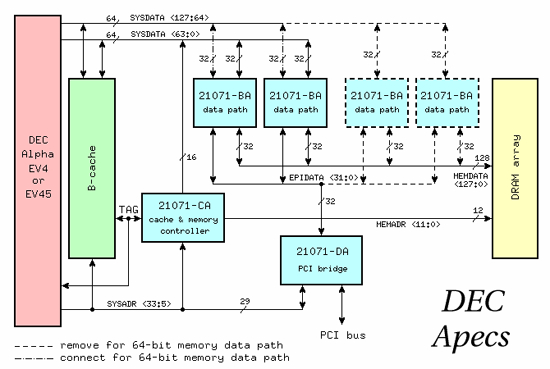

Первые чипсеты для EV4 использовали периферийные шины TURBOchannel, FutureBus+ и XMI. Хотя все эти реализации были очень скоростными для своего времени (около 100Мб/с на шину), они не получили широкого распространения, и количество доступной периферии измерялось единицами. Поэтому DEC обратила внимание на стандартные шинные архитектуры, такие как PCI и ISA (EISA). В начале 1994 был представлен чипсет DEC Apecs в двух исполнениях: с 64-битной системной шиной данных (21071) и 128-битной (21072). Вся разница между ними состояла в том, что 21071 состоял из 4 микросхем (1 универсальный контроллер, 2 микросхемы data slice, 1 контроллер шины PCI), а 21072 -- из 6 (дополнительно ещё 2 микросхемы data slice). Поддерживал частоту системной шины в 33МГц, до 16Мб B-cache и до 4Гб памяти FPM parity со временем доступа от 100 до 50нс. Поддержка шин ISA или EISA могла быть реализована посредством стандартных мостов, таких как i82378IB (ISA) или i82378EB (EISA).

Первая рабочая станция архитектуры Alpha от DEC была выпущена в ноябре 1992, DEC 3000 Model 500 AXP (кодовое имя Flamingo), с процессором EV4 150МГц, 512Кб B-cache, 32Мб оперативной памяти, SCSI HDD на 1Гб, SCSI CD-ROM, встроенным контроллером Ethernet 10Мбит (толстый коаксиал и витая пара), встроенным звуковым и ISDN контроллером, а также с 19-дюймовым монитором (1280х1024 8-бит). Цена была шокирующая: 38995 долл. США.

Часть 5. EV5, EV56, PCA56, PCA57

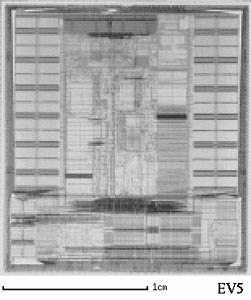

Первая архитектурная информация о своём Alpha-процессоре 2-го поколения была открыта DEC на конференции Hot Chips, которая состоялась 14 августа 1994 в Пало-Альто (Калифорния), хотя официальным анонсом21164(EV5) можно считать пресс-релиз DEC от 7 сентября 1994. Процессор базировался на ядре EV45 и содержал изменения скорее экстенсивного характера, чем интенсивного. Ядро включало удвоенное количество конвейеров для целочисленной и вещественной математики (по сравнению с EV4 или EV45), причём количество стадий вещественных конвейеров сократилось с 10 до 9. Однако, целочисленные конвейеры были неодинаковы: хотя оба могли выполнять элементарные арифметические и логические операции, только в компетенцию 1-го входило выполнение инструкций умножения и смещения, и только по 2-му могли быть направлены инструкции условных/безусловных переходов; также, оба конвейера могли вычислять виртуальные адреса для команд загрузки, однако только 1-й -- для команд сохранения. Вещественные конвейеры были также неоднородны: 1-й мог выполнять любой код с плавающей запятой, кроме инструкций умножения, которые были теми единственными командами, что мог выполнять 2-й конвейер. Чтобы обеспечить эффективную загрузку функциональных устройств, I-box мог выбирать и декодировать до 4 инструкций за такт. Производился по тому же 4-слойному 0,5µ CMOS5 техпроцессу, что и EV45, был рассчитан на напряжение питания в 3,3В, имел площадь ядра в 299 кв.мм. и содержал 9,3 млн. транзисторов (из них 7,8 млн. в виде интегрированного кэша), что было очень близко к теоретическому пределу для данного техпроцесса. Тактовые частоты EV5 составляли от266МГц до 333МГц(TDP от 46Вт до 56Вт). Форм-фактор: IPGA-499 (Interstitial Pin Grid Array).

Размеры и организация I-cache и D-cache остались как у EV4, то есть по 8Кб, и со сквозной записью для D-cache, хотя он теперь стал двухпортовым по чтению, то есть за 1 такт он мог поставить данные для 2 инструкций загрузки. Жертвуя транзисторами во имя быстродействия, физически D-cache состоял из 2 абсолютно одинаковых по содержанию частей размером в 8Кб каждая, то есть чтение шло из любой части, а запись -- одновременно в обе. Так как процессор имел 96Кб интегрированного кэша L2 с обратной записью с 3-канальной ассоциативностью, то в структуру C-box была добавлена его поддержка (S-cache, secondary cache) через независимую 128-битную шину данных, при этом интерфейс к внешнему B-cache (который все ещё оставался опциональным, набирался на микросхемах синхронной статической памяти и мог иметь размер до 64Мб, хотя обычно составлял от 1Мб до 4Мб) был сохранён -- другими словами,EV5 поддерживал 3 уровня кэшей. Доступ к S-cache был организован по принципу 4-стадийного конвейера: два такта на поиск тега и его изменение, два такта на доступ к данным и их передачу; строка S-cache была в 64 байта (с возможным разделением на две 32-байтных подстроки), с одним тегом на строку. Задержки при чтении из D-cache сократились до 2 тактов, а из S-cache -- составляли 7 тактов (как упоминалось выше, 4 такта на первые 16 байт, и по 1 такту на каждые последующие 16 байт для формирования полной строки). Как и в EV4, содержимое D-cache дублировалось, только теперь в S-cache; в свою очередь, для упрощения поддержки, B-cache был включающим S-cache, несмотря на разницу в ассоциативностях. Ёмкость I-TLB была увеличена до 48 записей (страницы размером от 8Кб до 4Мб), а D-TLB -- до 64 записей, причём он стал двухпортовым (по аналогии с D-cache). Системная шина данных имела фиксированную ширину в 128 бит (с дополнительными 16 битами для ECC) и всё так же мультиплексировалась с шиной данных к B-cache; системная шина адреса была 40-битной, управления -- 10-битной.

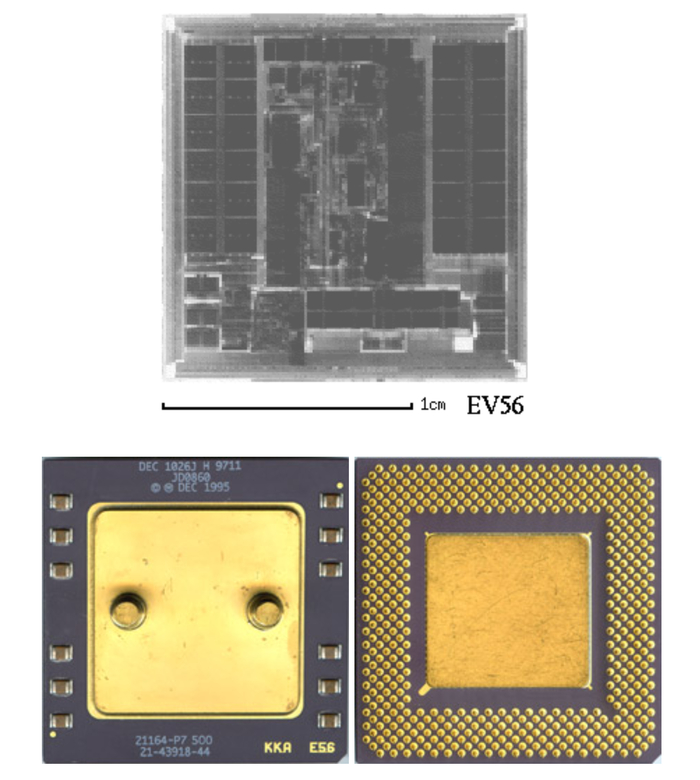

В октябре 1995, на Microprocessor Forum, был представлен 21164А (EV56), незначительно модифицированная версия EV5 с учетом 0,35µ конструкторских норм (CMOS6), производимая на той же фабрике в Хадсоне (DEC инвестировала в её модернизацию около 450 млн. долл США). Наиболее существенным архитектурным отличием можно считать BWX (Byte-Word Extension) -- набор из 6 дополнительных команд для загрузки/сохранения данных размером в 8 или 16 бит. Изначально архитектура Alpha поддерживала загрузку/сохранение данных квантами исключительно по 32 или 64 бита, что создавало определенные сложности при портировании или эмуляции кода других процессорных архитектур, например, i386 или MIPS. Предложение о внедрении BWX в базовый набор команд Alpha появилось в июне 1994 с подачи Ричарда Сайтса и было утверждено в июне 1995. Правда, для успешной работы BWX требовалась поддержка как со стороны процессора, так и со стороны чипсета. EV56 производился с тактовыми частотами от 366МГц до 666МГц (TDP от 31Вт до 55Вт), начиная с лета 1996. Samsung также выпускал EV56, по лицензионному соглашению с DEC от июня 1996 (версию на 666МГц производил только он). Содержал 9,66 млн. транзисторов, площадь ядра составляла 209 кв.мм., использовалось двойное напряжение (2,5В на основную логику и 3,3В на входные-выходные цепи).

17 марта 1997 был представлен 21164PC (PCA56), бюджетный вариант EV56, спроектированный совместно DEC и Mitsubishi. Отсутствовал S-cache и соответствующая логика, зато размер I-cache был увеличен вдвое (до 16Кб). Содержал 3,5 млн. транзисторов, имел площадь ядра в 141 кв.мм., использовал тот же техпроцесс и напряжение питания, что и EV56; форм-фактор процессора изменился: IPGA-413 против IPGA-499. Выпускался с тактовыми частотами от 400МГц до 533МГц (TDP от 26Вт до 35Вт). В будущем, на производственных мощностях Samsung, также выпускался 0,28µ вариант 21164PC (PCA57), с удвоенными размерами I-cache и D-cache, причём первый использовал 2-канальную ассоциативность. Количество транзисторов в ядре увеличилось до 5,7 млн., а его площадь уменьшилась (до 101 кв.мм.); был спроектирован под пониженное напряжение питания (2,0В на основную логику и 2,5В на входные-выходные цепи), с тактовыми частотами от 533МГц до 666МГц (TDP от 18Вт до 23Вт).

Кроме унаследованных от EV56 инструкций BWX, PCA56 поддерживал новый набор MVI (Motion Video Instructions), предназначенный для ускорения алгоритмов обработки видео и аудио потоков по принципу SIMD (Single Instruction -- Multiple Data), в некоторой мере сопоставимый с MMX.

Первым стандартным чипсетом, разработанным для EV5, был DEC Alcor (21171). Он поддерживал частоту системной шины в 33МГц, до 64Мб B-cache, до 8Гб памяти FPM ECC (используя шину памяти разрядностью в 256 бит), а также 64-битную шину PCI (33МГц). Поддержка шины ISA (EISA) могла быть реализована посредством стандартного моста, как и прежде. Встроенного контроллера IDE также не было (мог устанавливаться отдельной микросхемой других производителей). Физически чипсет состоял из 5 чипов: 1 универсального контроллера (включающего поддержку шины PCI), и 4 коммутаторов данных (data switch). Одновременно с запуском в производство EV56 была выпущена модификация Alcor, поддерживающая BWX -- Alcor 2 (21172). Дальнейшим развитием этой "чипсетной династии" стал одночиповый Pyxis (21174), который поддерживал системную шину с частотой в 66МГц и память SDRAM ECC 66МГц (правда, используя шину памяти с разрядностью в 128 бит). Для систем на основе PCA57 был разработан чипсет VLSI Polaris.

В виду ограничения количества символов в статье

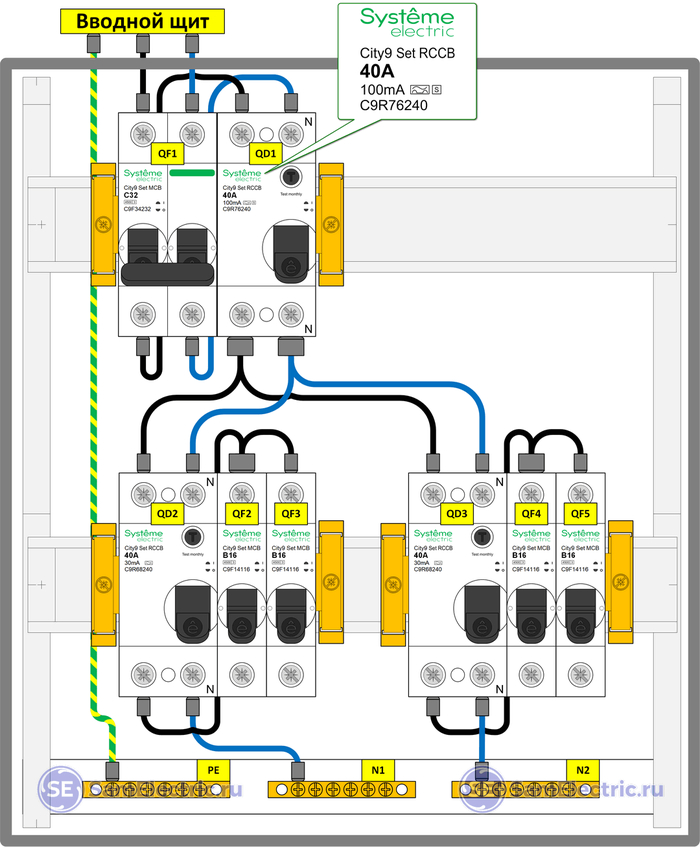

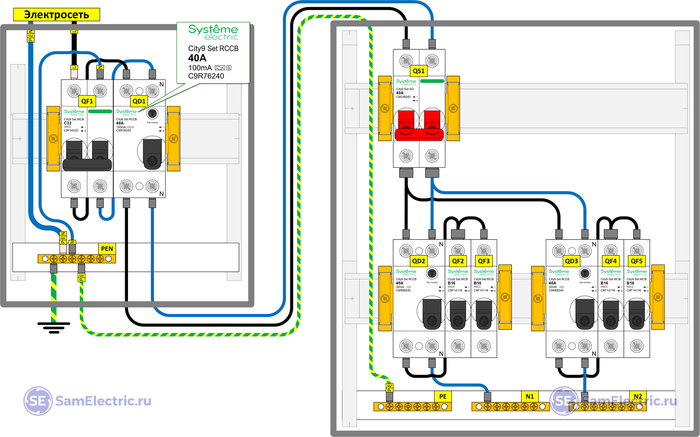

![12.09.1994 — Презентация браузера «Mosaic Netscape» [вехи_истории] Информатика, Технологии, Инженер, История IT, Вехи истории, Информатика Алексей Гладков, Web, Netscape, Netscape navigator, Браузер, Веб-разработка, Длиннопост](https://cs20.pikabu.ru/s/2025/09/10/22/iep2wjvf.jpg)

![12.09.1994 — Презентация браузера «Mosaic Netscape» [вехи_истории] Информатика, Технологии, Инженер, История IT, Вехи истории, Информатика Алексей Гладков, Web, Netscape, Netscape navigator, Браузер, Веб-разработка, Длиннопост](https://cs19.pikabu.ru/s/2025/09/10/22/iepuwmoo.jpg)

![12.09.1994 — Презентация браузера «Mosaic Netscape» [вехи_истории] Информатика, Технологии, Инженер, История IT, Вехи истории, Информатика Алексей Гладков, Web, Netscape, Netscape navigator, Браузер, Веб-разработка, Длиннопост](https://cs20.pikabu.ru/s/2025/09/10/22/iip2xcs7.jpg)